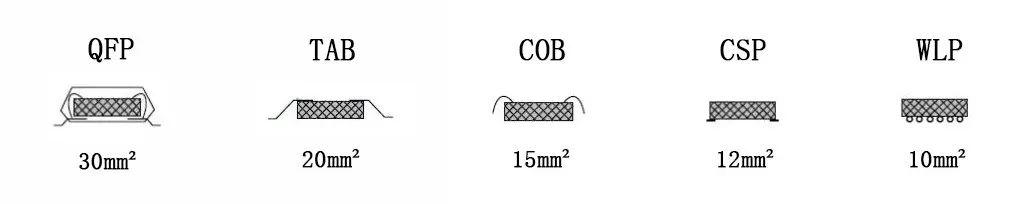

5G时代下,各类消费电子产品趋向轻巧、多功能、低功耗发展,半导体封装正向着高度集成的方向发展。

而为了在更小的封装面积下容纳更多的引脚数,晶圆级封装(WLP)也开始受到越来越多的关注。

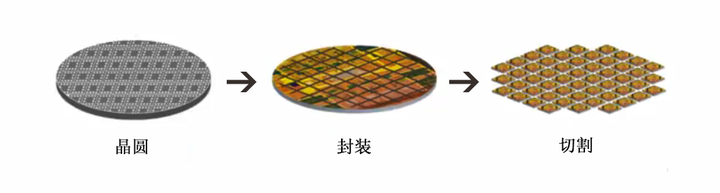

晶圆级封装,即将晶圆作为加工对象,直接在整片晶圆上进行CSP封装及测试,最后再切割成单个器件,同时具备更多的功能集成,尺寸也更小,可直接贴装到基板或印刷电路板上。

这样改变之后,芯片设计和封装设计就能统一考虑,能够简化供应链、缩短生产周期且降低成本。

目前所谓的晶圆级封装一般分为Fan-in和Fan-out两种,下面展开讲讲。

Fan-in封装即标准的WLP工艺,封装后的尺寸与IC裸晶的原尺寸几乎等同,直接贴装到基板或印刷电路板上,大大降低加工成本、提升加工效率。

由于中间没有载体,焊球直接植于硅基材上,其敏感度远超BGA,有效增加了数据传输的频宽并减少了信号损耗,数据传输速度和稳定性大幅提升;同时没有塑封料或陶瓷包封,其散热能力也更强。

Fan-in封装已成为目前移动/消费应用的主流封装技术,与基于基板的封装相比,它提供了成本更低的解决方案。

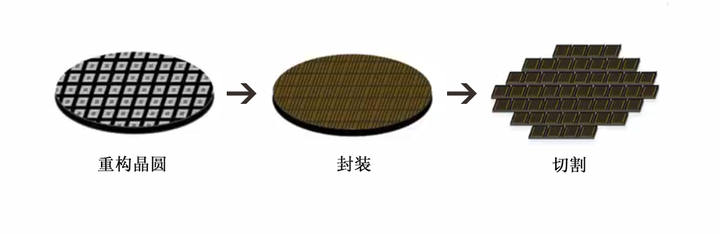

Fan-out封装是基于晶圆重构技术,将测试合格的芯片重新埋置到晶圆上,然后按照与标准WLP 工艺类似的步骤进行封装,得到的实际封装面积要大于裸晶。

由于实际封装面积要大于芯片面积,在面积扩展的同时也可以增加其它有源器件及无源元件,形成SiP。

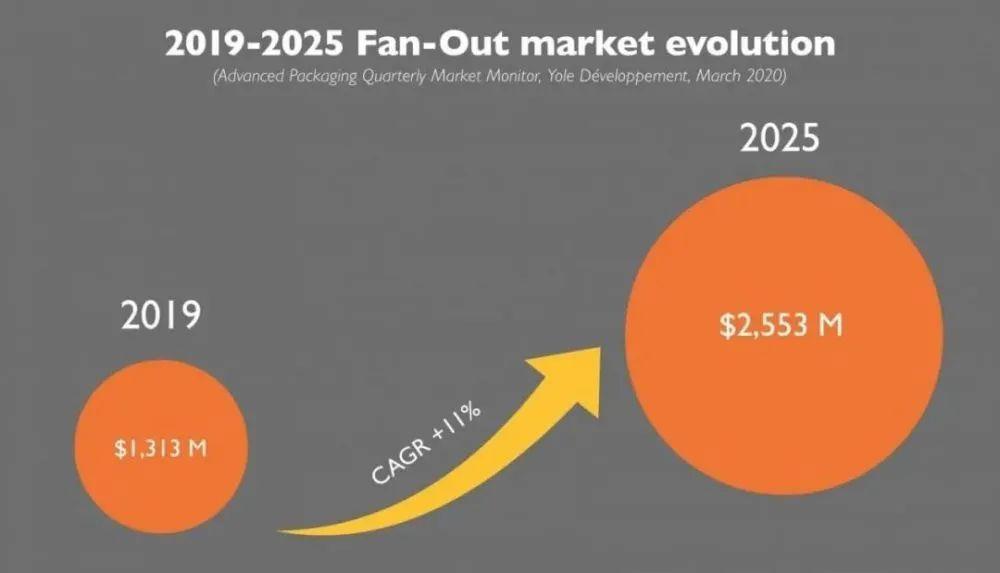

Fan-out封装可实现小芯片和异构集成,预计将在未来几年内随着5G、AI和自动驾驶的发展得到普及。

先进封装技术已经成为高性能芯片的必选项,在可预见的未来,晶圆级封装对传统封装技术的替代将成为趋势。

从上文我们可以看到,晶圆级封装与传统封装最关键的区别就是——将封装好的晶圆切割成片后,直接贴装到基板或印刷电路板上,单个元件体积缩小了数倍。

不仅如此,晶圆级封装的焊球直径更小,焊球间距更小(范围在0.3mm-0.5mm之间),所以在固晶时需要更精准的对位及取放压力。

这意味着,采用更柔性、更好控制的高精度电机来进行操作,才更能匹配先进晶圆封装的贴装需求。

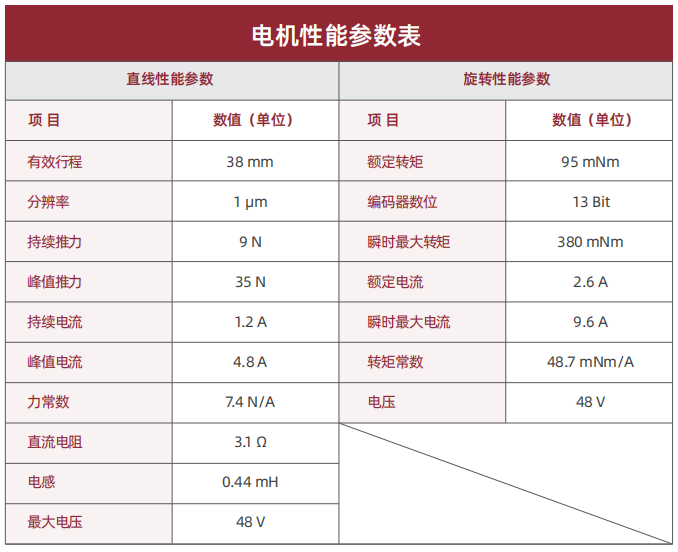

国奥直线旋转电机助力提供更柔性固晶方案,双向线性致动器和软着陆能够精准地控制力量,重复定位精度可达+/- 2μm,能更轻柔地触碰晶片表面,进行准确的真空取放。

±0.01N的精准力控处于全球领先水平,协助提升生产设备的柔性化程度,提高生产效率和产品良率,共计申请相关核心专利知识产权和软件著作权100余项。

国奥电机致力于为半导体封测、精密制造、智慧医疗、3C自动化等产业领域提供先进装备及解决方案,欢迎预yue选型~

*博客内容为网友个人发布,仅代表博主个人观点,如有侵权请联系工作人员删除。